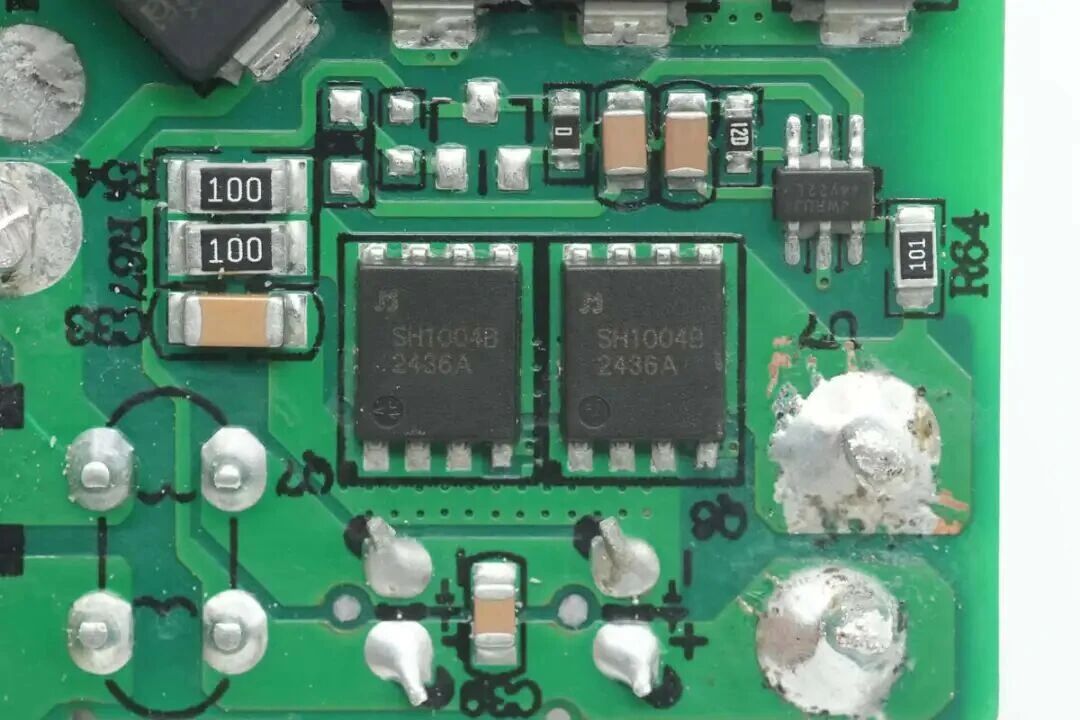

驱动芯片

驱动芯片(Driver Chip)是一种集成电路芯片,用于控制和驱动其他电子器件的工作。它通常被用于激活、控制和管理各种类型的设备,如电机、LED灯、显示屏等。驱动芯片可以提供所需的电压、电流和信号,以确保外部设备能够正常运行。

驱动芯片是一种专门设计用于控制和驱动其他电子器件的集成电路芯片。它通过接收来自主控制器或其他输入源的指令和信号,提供所需的电力和信号,以使得被控制的设备按照预定的方式工作。

驱动芯片通过集成了电路功能和控制逻辑,能够对外部设备进行控制和管理。它可以提供不同的接口和协议,以适应不同类型的设备和应用需求。驱动芯片的设计和功能根据具体的应用场景而变化,例如电机驱动芯片、LED驱动芯片、显示芯片等。

驱动芯片在电子系统中起着至关重要的作用。它可以完成以下功能:

1、控制信号转换和放大

驱动芯片能够接收来自主控制器或其他输入源的控制信号,并将其转换为适合被控制设备的信号。它可以对输入信号进行放大、缓冲和滤波处理,以确保设备能够正常工作。

2、电力供应和电流驱动

驱动芯片能够提供所需的电压和电流,以满足被控制设备的电力需求。它可以通过内部的电源管理电路,稳定输出电压和电流,并根据需要进行调整和保护。

3、接口协议支持

驱动芯片可以支持不同的接口协议,以实现与其他设备的通信和数据交换。它可以提供串行通信接口(如I2C、SPI)、并行接口(如GPIO)等,使得主控制器能够与外部设备进行有效的信息传递和数据交互。

4、保护和安全功能

驱动芯片通常具有各种保护功能,以确保设备的安全和可靠性。例如过流保护、过温保护、短路保护等,可以防止设备受到损坏或故障。

驱动芯片的工作原理基于集成电路的技术和设计。它通常由多个功能模块组成,包括控制逻辑、信号转换、电源管理和输出驱动等。

驱动芯片首先接收来自主控制器或其他输入源的指令和信号。控制逻辑模块对这些信号进行处理和解码,根据预定的算法和规则生成相应的控制信号。

信号转换模块将控制信号转换为适合被控制设备的信号。它可以通过放大电路放大信号的幅度,并通过滤波电路去除噪声和干扰,以确保输出信号的稳定性和准确性。

电源管理模块负责提供所需的电压和电流。它通过内部的电源调节器和稳压器等电路,将输入电压转换为稳定的输出电压,并根据需要进行电流调整和保护。

输出驱动模块是驱动芯片最重要的部分,它将经过处理的控制信号转化为能够驱动被控制设备的电力信号。输出驱动模块通常包含功率放大器、晶体管、继电器等元件,能够提供足够的电流和功率,以使得被控制设备正常工作。

驱动芯片还可以具有其他功能模块,如接口控制、保护电路和诊断功能等。这些功能模块可以增强驱动芯片的功能和安全性。

在线留言询价

中国台湾对南非限制芯片出口,外交部回应!

一文了解芯片的制造流程

- 一周热料

- 紧缺物料秒杀

| 型号 | 品牌 | 询价 |

|---|---|---|

| CDZVT2R20B | ROHM Semiconductor | |

| MC33074DR2G | onsemi | |

| RB751G-40T2R | ROHM Semiconductor | |

| BD71847AMWV-E2 | ROHM Semiconductor | |

| TL431ACLPR | Texas Instruments |

| 型号 | 品牌 | 抢购 |

|---|---|---|

| IPZ40N04S5L4R8ATMA1 | Infineon Technologies | |

| ESR03EZPJ151 | ROHM Semiconductor | |

| TPS63050YFFR | Texas Instruments | |

| STM32F429IGT6 | STMicroelectronics | |

| BU33JA2MNVX-CTL | ROHM Semiconductor | |

| BP3621 | ROHM Semiconductor |

AMEYA360公众号二维码

识别二维码,即可关注

请输入下方图片中的验证码: