- Ameya360 Component Supply Platform >

- Trade news >

- 全面剖析我国集成电路产业人才现状、缺口及发展建议

全面剖析我国集成电路产业人才现状、缺口及发展建议

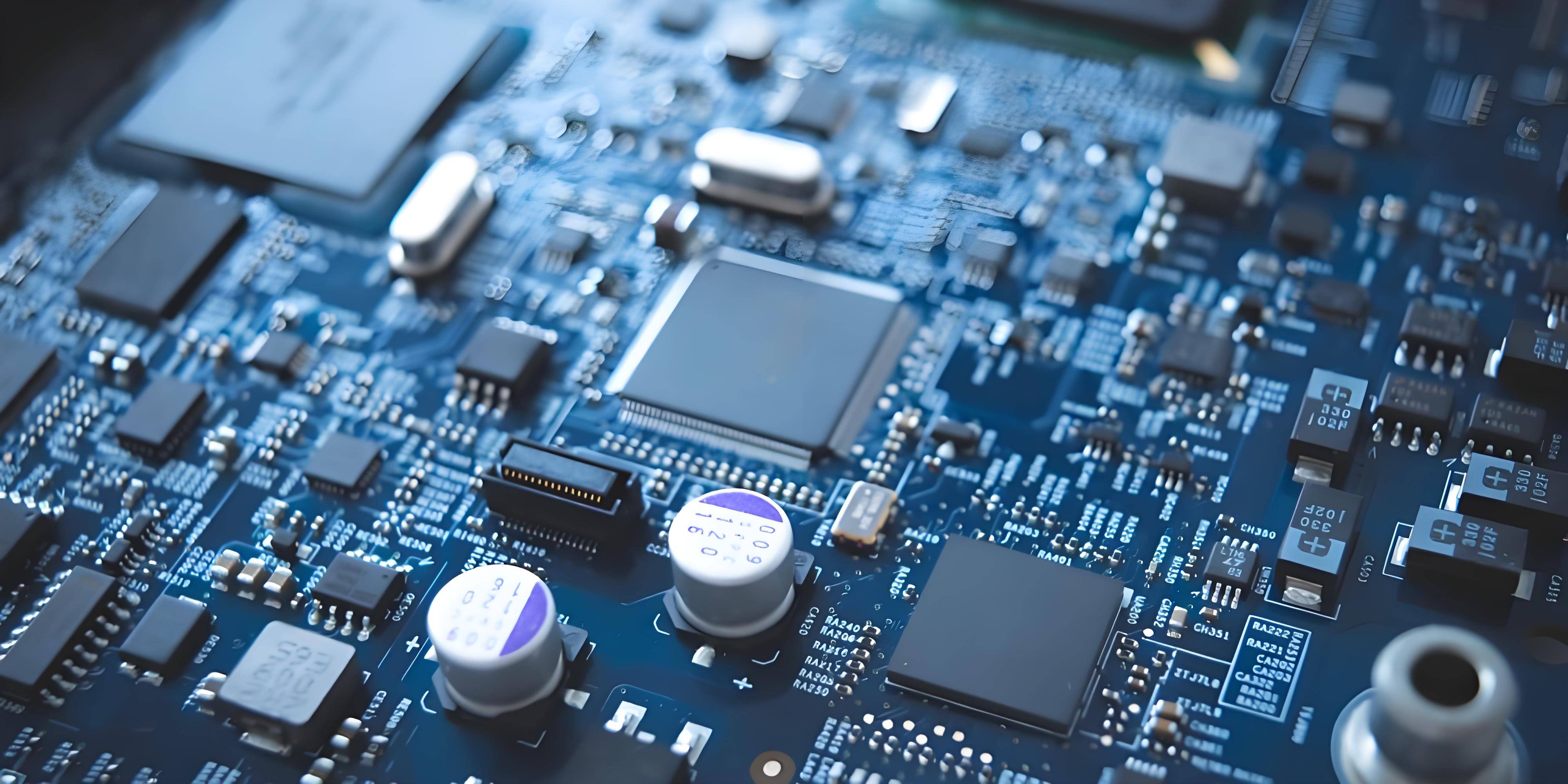

当前,我国集成电路产业与国际先进水平的差距正在逐步缩小,但逐渐凸显出的人才短缺问题成为了横亘在半导体产业追逐之路上的一大障碍和挑战。

集成电路产业人才现状

据上海华虹宏力半导体公司执行副总裁徐伟报告数据显示,截至2017年底,我国集成电路行业从业人员规模在40万人左右。其中,设计业、制造业、封装测试业从业人数分别为14万、12万、14万。

集成电路是一个人才密集的产业,对人才数量和质量都有很高的要求。

技术人员在企业员工总数中的占比很高,我国集成电路行业技术类从业人员规模为33万人左右,占总从业人数的83%左右。其中,集成电路生产企业(含制造和封装)的技术人员比例超过50%,而芯片设计企业的技术人员比例高达80%以上。

数据来源:徐伟演讲报告

集成电路产业从业人员总体学历较高,通常要求从业人员具备一定的学习能力和知识结构,从2017-2018年从业人员的学历结构来看,本科学历占比65%,其次是硕士和大专。设计企业中,研发人员占80%左右,研发人员中80%左右具备硕士及以上学历。

人才供给及缺口

人才供给方式

目前,我国人才供给主要来源于国内高校培养、高端人才引进、社会培训以及企业自主培养等几种方式。

学校培养

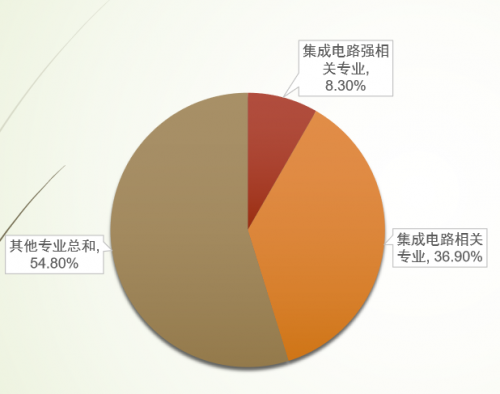

全国本科院校中集成电路相关专业开设情况如下图

数据来源:中国教育在线高校数据库,CSIP整理

从业人员除了集成电路专业领域的毕业生外,还需要物理、化学、材料、机电、软件、电子学、生物等其他专业的毕业生。

从去年从业人员所在的专业属性来看:集成电路专业领域的从业人员占比为45%左右,其中与集成电路强相关的专业占比为8.3%,相关的专业占比为36.9%其他专业占比为54.8%,包括计算机、物理、电气、自动化等。

数据来源:白皮书编委会调研数据、智联招聘全站大数据,CSIP整理

高端人才引进

目前国内很多高端领军集成电路人才来自海外,这些专家取得的创新成果已引起国内外同行的广泛关注,得到了社会各界的高度认可,并在各自领域作出了显著成绩,成为国家创新创业生力军。

社会培训

集成电路高级研修班、急需紧缺人才培养班;集成电路专业中高级职称评审;社会培训机构等,加大开展大规模职业技能培训和建立对全社会开放的培训平台,推动国内集成电路产业人才的培养和能力的持续提升,适应产业快速发展的需要。

企业自主培养

每家企业均应注重“选用育留”,自主培养,育秀成才,种树成林,从而扩大产业人才规模,形成良性的人才生态体系。

人才缺口现状

人才缺口大,既缺少技术人员,也缺乏领军人才

据不完全统计,我国目前在建集成电路生产线25条以上,到2020年前后,我国集成电路行业人才需求规模约为72万人左右,而我国现有人才存量40万人(设计业14万人,制造业12万人,封测业14万人),人才缺口将达到32万人。

专业领域的毕业生人数在20万左右,但是不足3万人进入集成电路行业从业。

虽然有计算机、物理、自动化等专业的毕业生流向集成电路行业,但单纯依托高校培养和输送人才无法满足产业对人才的需求。大幅提升集成电路专业的招生人数已经迫在眉睫。

人才抢夺激烈,不乏恶意竞争

由于产业迅速发展,人才缺口巨大,国内企业想尽办法吸引人才,对于人才出现恶意竞争的现象,并导致企业用人成本急剧攀升。

芯片人才供给为何赶不上需求?

薪资低

目前国内芯片行业由于投入产出比比较大、研发投入高企等因素,企业利润有限,人才薪资不及其他行业。

招聘网站发布的《2019年芯片人才数据洞察》显示,芯片行业的人才薪资低,2019年芯片行业人才平均招聘薪资为10420元,十年工作经验的芯片人才平均招聘工资为19550元,仅为同等工作年限的软件类人才薪资水平的一半。

成长速度慢、迭代周期长是限制芯片人才薪资涨幅的重要原因之一。此外,一位集成电路投资人也认为,企业需要的优秀人才是能够直接上手的,而刚毕业的学生需要大量的培训、长时间的沉淀,两者相差甚远。一位高校老师表示,企业不太愿意接收短期学生实践,即使接收也会以涉密为由不给学生充分的锻炼机会。

同时,薪资低也是制约跨行业择业的限制因素。

人才供给不足

上面提到,当前国内芯片人才面临巨大缺口,需求量大,但供给不足。

事实上,除了人才缺失,集成电路行业人才流失率较高也成业内普遍存在的问题。多年来的低薪环境导致芯片从业人员对自身岗位薪资预期普遍偏低,大部分集成电路专业高校毕业生更愿意去互联网、计算机软件、IT服务、通信和房地产等行业。

集成电路产业人才发展建议

加大高校培养力度

集成电路行业是一个对于知识体系、能力结构和实践经验要求较高的行业,高校作为人才培养的主阵地,建议加快推动微电子和集成电路相关一级学科建设,增强高校集成电路人才实践能力,缩小高校人才培养与企业用人需求间的差距,积极推动集成电路人才的“供给侧结构性改革”。

明确人才培养标准,开展大规模职业教育培训

大力发展职业培训并开展继续教育活动,采取多种形式大力培养和培训集成电路领域高层次、急需紧缺和骨干专业技术人才。

推行集成电路人才优惠政策

进一步完善鼓励创新创造的分配激励机制,落实科技人员科研成果转化的股权、期权激励和奖励等收益分配政策,特别是对于集成电路行业人才在个人所得税方面可以有适当减免和优惠政策。

加强海外高端人才引进力度,构建国际智库合作交流平台

加大海外高层次人才引进力度,为高端人才的引进创造有利宽松的环境。

构建集成电路相关领域创新创业的生态体系,吸引更多跨专业人才进入集成电路领域

Previous: ARM发布Cortex-A77与Mali-G77架构,效能大升级

Online messageinquiry

集成电路的概念及分类

“芯”为何物?一篇关于集成电路的详细解读

- Week of hot material

- Material in short supply seckilling

| model | brand | Quote |

|---|---|---|

| MC33074DR2G | onsemi | |

| BD71847AMWV-E2 | ROHM Semiconductor | |

| CDZVT2R20B | ROHM Semiconductor | |

| TL431ACLPR | Texas Instruments | |

| RB751G-40T2R | ROHM Semiconductor |

| model | brand | To snap up |

|---|---|---|

| BP3621 | ROHM Semiconductor | |

| ESR03EZPJ151 | ROHM Semiconductor | |

| TPS63050YFFR | Texas Instruments | |

| IPZ40N04S5L4R8ATMA1 | Infineon Technologies | |

| BU33JA2MNVX-CTL | ROHM Semiconductor | |

| STM32F429IGT6 | STMicroelectronics |

Qr code of ameya360 official account

Identify TWO-DIMENSIONAL code, you can pay attention to

Please enter the verification code in the image below: