- Ameya360 Component Supply Platform >

- Trade news >

- 上海集成电路产业2017年“双丰收” 销售规模近1200亿元

上海集成电路产业2017年“双丰收” 销售规模近1200亿元

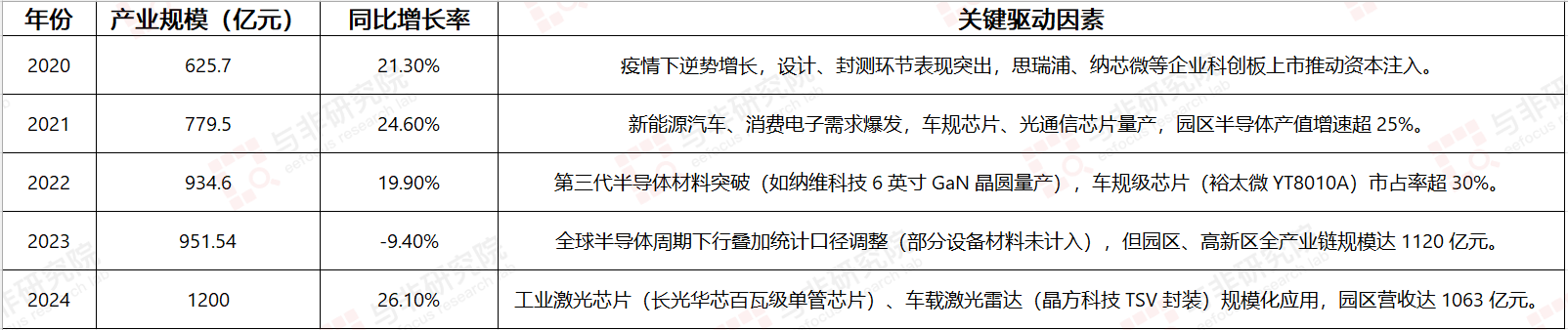

上海集成电路产业去年实现速度质量“双丰收”。日前上海市经济和信息化委公布,2017年上海市集成电路产业整体销售规模接近1200亿元,同比增长超过12%,产业链结构更加优化,设计、制造、装备材料“三足鼎立”的态势基本形成。

据初步统计,2017年上海市芯片设计业实现销售约440亿元,同比增长近20%;芯片制造业实现销售近300亿元,同比增长约8%;装备材料业实现销售超过150亿元,同比增长超过30%,带动了本市集成电路产业快速发展。

尤其是在集成电路设计业的发展,上海实现了速度和质量双轮驱动。据介绍,设计业是产业链龙头,也是面向应用的最终环节。上海一直高度关注本市集成电路设计业的发展,通过研发资助、研发人员奖励、核心团队奖励、税收优惠等一系列产业政策,扶持设计业在沪快速壮大。

从产业规模看,2010年上海集成电路设计业规模突破100亿、2013年突破200亿、2015年突破300亿、2017年突破400亿,近10年的年均复合增长率超过25%、增加近10倍。从企业数量和规模看,2017年本市设计企业共239家,相比2016年增加24家,其中年销售收入过亿元的共50家,超10亿元的共8家。

值得一提的是,上海集成电路的核心技术能级已接近世界领先水平,逻辑电路主流设计技术为40-28-16/14nm,先进设计技术已进入10nm、7nm设计技术正在研发;数模混合电路、模拟电路等设计技术在国内均处于领先行列。2017年,展讯通信推出14nm、8核、64位LTESoC智能手机芯片,支持五模全频段通信;并率先完成5G原型机开发,在5G标准化及商用化进程上与国际一流水平保持同步。

上海经信委相关负责人表示,目前上海市集成电路产业提出了“二次布局、二次创业,引领产业跨向2000亿大关”的发展目标,将通过“提升产业发展战略,塑造设计、制造、装备材料三大支柱。同时拓展产业发展模式,打造IDM模式的产业第三极;引导核心企业实现集团化发展,加强对外合作和对接;推动集成电路产品多样化差异化,支持产业向泛半导体领域扩展;完善产业区域布局,加快产业向临港、嘉定等区域外延”的发展手段,推进本市集成电路产业加速发展。

回顾上海半导体2017年十大事件 :

一、《关于本市进一步鼓励软件产业和集成电路产业发展的若干政策》发布

2017年完成《软件和集成电路专项资金管理办法》、《上海集成电路工程产品首轮流片专项奖励实施细则的》等相关配套实施细则的编制并发布,为集成电路产业的发展营造了良好的政策环境。在原有基础上,进一步聚焦支持上海集成电路领域重大项目建设、自主创新技术研发、企业培育和专业人才培养及引进等方面。

二、500亿集成电路产业基金启动

7月21日,总规模100亿元的上海集成电路装备材料基金签约仪式在上海临港举行,这是继100亿设计业并购基金和300亿制造业基金之后,上海完成组建的第三支集成电路产业基金,这标志着上海500亿元集成电路产业基金工作已全面启动,并正式进入运营阶段,也是上海加快实体经济建设的重要举措。

三、加快平台建设助力产业腾飞

2017年集成电路研发与转化功能性平台入选首批4个市级功能性平台,正在加紧建设。同时加快推动国家集成电路制造业创新中心、国家MEMS传感器制造业创新中心落地上海。

四、重大项目建设稳步推进

华力二期项目提前3个月实现主厂房结构封顶;和辉二期项目提前2个月完成年度投资任务,预计全年可超额完成30%以上;中芯南方项目完成地上建筑审批手续,启动主厂房施工。

五、中国电子与上海市战略合作投资1000亿元

12月12日,中国电子与上海市签署战略合作协议,双方将联合组织投资1000亿元,围绕集成电路、智能制造、科创园区、新型智慧城市等领域展开全面合作。

六、国产桌面计算机绽放光彩

9月,上海兆芯CPU的国产整机获得“十九大”会议采购近600台,国产整机在会议期间运行稳定,机器性能良好、易用性强,凸显了上海集成电路产业自主研发设计的实力。

七、9家电子信息制造企业上市

2017年电子信息企业挂牌上市的企业达到9家,其中盛美半导体设备(上海)有限公司11月3日在美国纳斯达克证交所正式挂牌上市,跻身美国资本市场。

八、中微进入台积电7nm刻蚀设备供应商

7月,台积电宣布中微半导体纳入其7nm工艺设备商采购名单。2017年中微半导体MOCVD设备进入大规模产业化,实现销售订单200台,设备发货106台,年收入10.6亿元,同比增长76.7%实现了爆发式增长。

九、中芯国际加速冲刺14纳米先进工艺

10月16日,中芯国际宣布梁孟松加入中芯国际,与赵海军共同出任联合首席执行官。梁孟松在半导体业界有着逾三十三年经历,从事内存储存器以及先进逻辑制程技术开发,此次加盟中芯国际,是中芯加速冲刺14nm新进工艺的又一重大事件。

十、国家重大科技项目300mm半导体硅片实现销售

新昇半导体继2016年拉出第一根12英寸(300mm)晶棒后,今年10月份开始已实现2.2万片(测试片)的月销售量,安装产能已达到每月4.5万片,初步打破大硅片完全依赖进口的局面。

Previous:富士康今天上会!供应商集体狂欢,跟着火了一把

Online messageinquiry

集成电路的概念及分类

“芯”为何物?一篇关于集成电路的详细解读

- Week of hot material

- Material in short supply seckilling

| model | brand | Quote |

|---|---|---|

| TL431ACLPR | Texas Instruments | |

| BD71847AMWV-E2 | ROHM Semiconductor | |

| RB751G-40T2R | ROHM Semiconductor | |

| MC33074DR2G | onsemi | |

| CDZVT2R20B | ROHM Semiconductor |

| model | brand | To snap up |

|---|---|---|

| STM32F429IGT6 | STMicroelectronics | |

| BP3621 | ROHM Semiconductor | |

| IPZ40N04S5L4R8ATMA1 | Infineon Technologies | |

| ESR03EZPJ151 | ROHM Semiconductor | |

| BU33JA2MNVX-CTL | ROHM Semiconductor | |

| TPS63050YFFR | Texas Instruments |

Qr code of ameya360 official account

Identify TWO-DIMENSIONAL code, you can pay attention to

Please enter the verification code in the image below: