全面掌握芯片散热设计基本概念

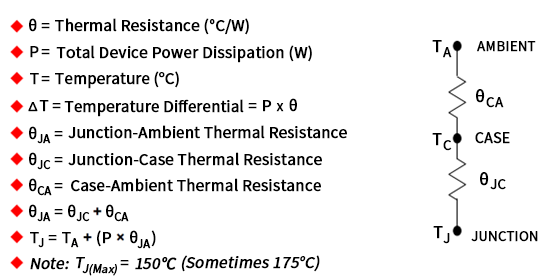

一般用符号θ来表示热阻。热阻的单位为℃/W。除非另有说明,热阻指热量在从热IC结点传导至环境空气时遇到的阻力。也可更具体地表示为θJA,即结至环境热阻。θJC和θCA是θ的两种其他形式,详见下文。

一般地,热阻θ等于100℃/W的器件在1W功耗下将表现出100℃的温差,该值在两个参照点之间测得。请注意,这是一种线性关系,因此,在该器件中,1 W的功耗将产生100℃的温差。再者对于热阻θ=95℃/W,因此,1.3 W的功耗将产生大约124℃结至环境温差。当然,预测内部温度时使用的正是这种温度的上升,其目的是判断设计的热可靠性。当环境温度为25°C时,允许约150℃的内部结温。实际上,多数环境温度都在25℃以上,因此,可以处理的功耗会稍低。

对于任意功耗P(单位:W),都可以用以下等式来计算有效温差(ΔT)(单位:℃):

ΔT = P ×θ

其中,θ为总适用热阻。下图总结了一些基本的热关系。

请注意,串行热阻(如右侧的两个热阻)模拟的是一个器件可能遇到的总热阻路径。因此,在计算时,总θ为两个热阻之和,即θJA = θJC + θCA。给定环境温度TA、P和θ,即可算出TJ。根据图中所示关系,要维持一个低的TJ,必须使θ或功耗(或者二者同时)较低。低ΔT是延长半导体寿命的关键,因为,低ΔT可以降低最大结温。

在IC中,一个温度参照点始终是器件的一个节点,即工作于给定封装中的芯片内部最热的点。其他相关参照点为TC(器件)或TA(周围空气)。结果又引出了前面提到的各个热阻,即θJC和θJA。

先来看看最简单的情况,θJA为在给定器件的结与环境空气之间测得的热阻。该热阻通常适用于小型、功耗相对较低的IC(如运算放大器),其功耗往往为1W或以下。一般而言,对于8引脚DIP塑封或者更优秀的SOIC封装,运算放大器以及其他小型器件的典型θJA值处于90-100°C/W水平。

需要明确的是,这些热阻在很大程度上取决于封装,因为不同的材料拥有不同水平的导热性。一般而言,导体的热阻类似于电阻,铜最好,其次是铝、钢等。因此,铜引脚架构封装具有最高的性能,即最低的θ。

上一篇:PCB元件焊接基本要点

下一篇:开关电源和变压器的区别是什么?

在线留言询价

一文了解逻辑芯片和处理器芯片的关系

科技部长阴和俊:芯片攻关取得新突破!

一文了解闪存芯片和ROM关系

- 一周热料

- 紧缺物料秒杀

| 型号 | 品牌 | 询价 |

|---|---|---|

| TL431ACLPR | Texas Instruments | |

| MC33074DR2G | onsemi | |

| CDZVT2R20B | ROHM Semiconductor | |

| BD71847AMWV-E2 | ROHM Semiconductor | |

| RB751G-40T2R | ROHM Semiconductor |

| 型号 | 品牌 | 抢购 |

|---|---|---|

| TPS63050YFFR | Texas Instruments | |

| STM32F429IGT6 | STMicroelectronics | |

| IPZ40N04S5L4R8ATMA1 | Infineon Technologies | |

| ESR03EZPJ151 | ROHM Semiconductor | |

| BP3621 | ROHM Semiconductor | |

| BU33JA2MNVX-CTL | ROHM Semiconductor |

AMEYA360公众号二维码

识别二维码,即可关注

请输入下方图片中的验证码: