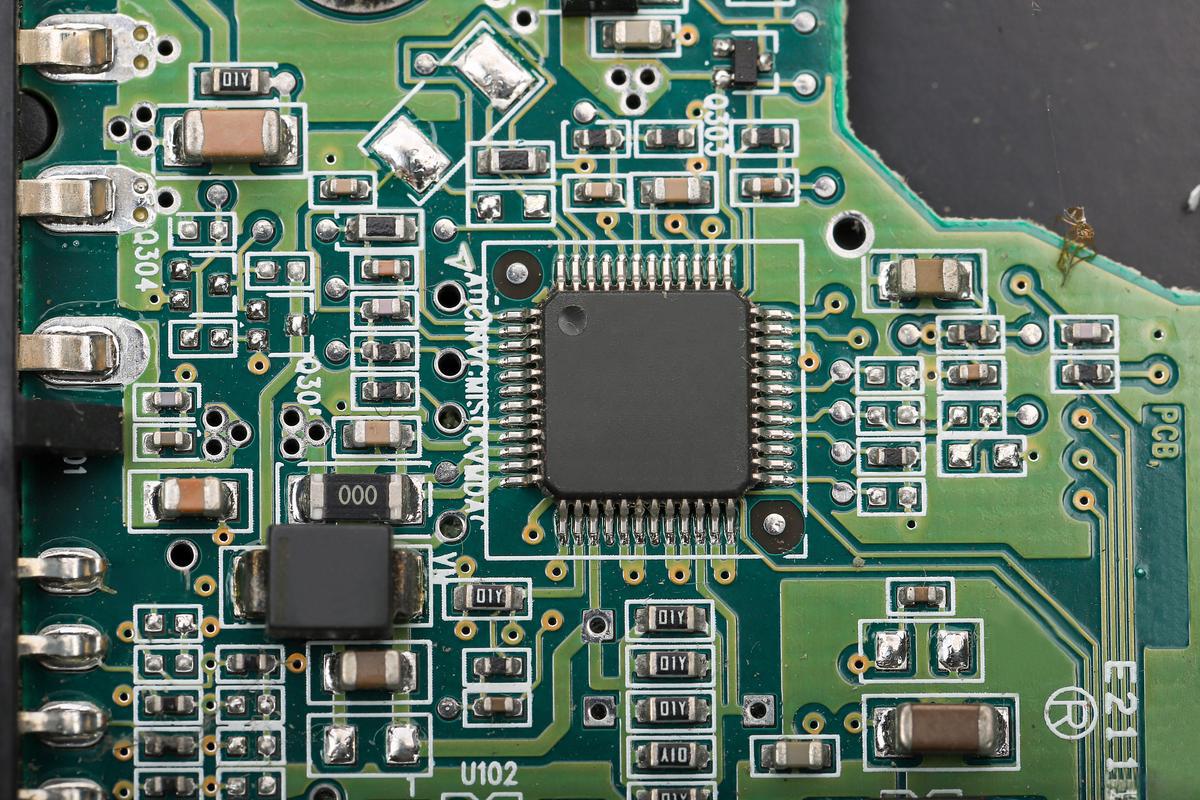

双面电路板

高科技发展,人们需要性能高、体积小、功能多的电子产品,促使印制线路板制造也向轻、薄、短、小发展,有限空间,实现更多功能,布线密度变大,孔径更小。

自1995 年至2005 年间,机械钻孔批量能力最小孔径从原来0.4mm 下降到0.2mm,甚至更小。金属化孔孔径也越来越小。层与层间互连所依赖的金属化孔,质量直接关系印制板可靠性。

随着孔径的缩小,原对较大孔径没影响的杂物,如磨刷碎屑、火山灰,一旦残留在小孔里面,将使化学沉铜、电镀铜失去作用,出现孔无铜,成为孔金属化的致命杀手。

钻头在敷铜板上先打孔,再经过化学沉铜,电镀铜形成镀通孔。二者对孔金属化起着至关重要的作用。

1、化学沉铜机理:

在双面和多层印制板制造过程中,都需要对不导电的裸孔进行金属化,亦即实施化学沉铜使其成为导体。化学沉铜溶液是一种催化式的“氧化/还原”反应体系。在Ag、Pb、Au、Cu 等金属粒子催化作用下,沉积出铜来。

2、电镀铜机理:

电镀定义是利用电源,在溶液中将带正电的金属离子,推送到位在阴极的导体表面形成镀层。电镀铜是一种“氧化/还原”反应,溶液中的铜金属阳极将其表面的铜金属氧化,而成为铜离子。另一方面在阴极上则产生还原反应,而令铜离子沉积成为铜金属。两者皆通过药水交换,化学作用达到孔化目的,交换效果好坏直接影响孔化质量。

在长期生产控制过程中,我们发现当孔径达到0.15-0.3mm,其塞孔的比例递增30%

1、孔形成过程中的塞孔问题:

印制板加工时,对0.15-0.3mm 的小孔,多数仍采用机械钻孔流程。在长期检查中,我们发现钻孔时,残留在孔里杂质

以下为钻孔塞孔的主要原因:

当小孔出现塞孔时,由于孔径偏小,沉铜前高压水洗、化学清洗难以把小孔里面的杂物去除,阻挡化学沉铜过程中药水在孔里的交换,使化学沉铜失去作用。

钻孔时根据叠层厚度选用合适钻嘴、垫板,保持基板清洁,不重复使用垫板,有效的吸尘效果(采用独立的吸尘控制系统)是解决塞孔必须考虑的因素。

在线留言询价

中国大陆百家集成电路设计公司!

模拟电路设计中噪声分析的误区及注意事项

- 一周热料

- 紧缺物料秒杀

| 型号 | 品牌 | 询价 |

|---|---|---|

| CDZVT2R20B | ROHM Semiconductor | |

| RB751G-40T2R | ROHM Semiconductor | |

| TL431ACLPR | Texas Instruments | |

| MC33074DR2G | onsemi | |

| BD71847AMWV-E2 | ROHM Semiconductor |

| 型号 | 品牌 | 抢购 |

|---|---|---|

| STM32F429IGT6 | STMicroelectronics | |

| BU33JA2MNVX-CTL | ROHM Semiconductor | |

| BP3621 | ROHM Semiconductor | |

| ESR03EZPJ151 | ROHM Semiconductor | |

| TPS63050YFFR | Texas Instruments | |

| IPZ40N04S5L4R8ATMA1 | Infineon Technologies |

AMEYA360公众号二维码

识别二维码,即可关注

请输入下方图片中的验证码: